JJHanna

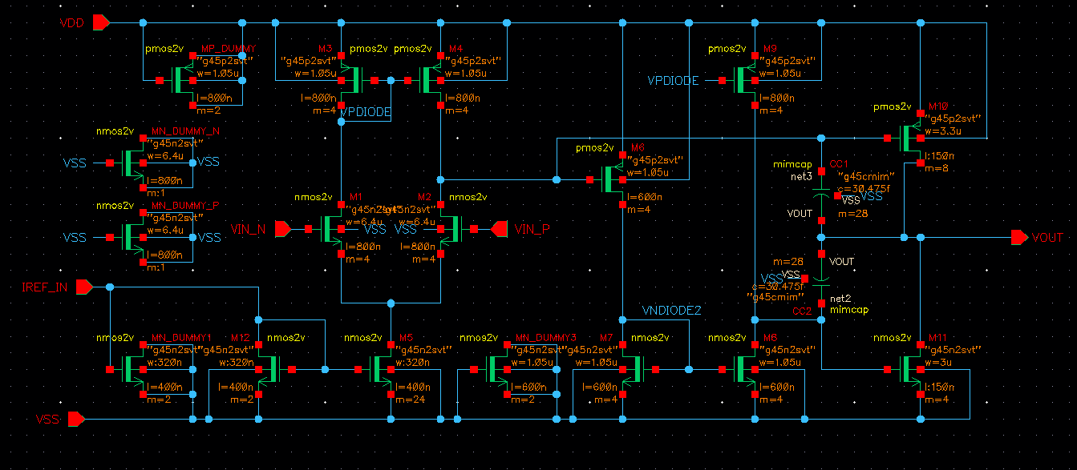

3 Stage Class-AB Common Source CMOS Op-Amp

This op-amp design features:

AOL Gain > 75 dB

Phase Margin ΦM > 50°

High Slew Rate > 20 V/µs

Low Offset < 1.5 mV

Unity-Gain Bandwidth > 25 MHz

Low Power Consumption < 500 µW

Near Rail-to-Rail Output Swing (0.01 V to 1.99 V)

High CMRR and PSRR & Low THD

Tested across PVT Corners and Monte Carlo

45 nm Technology with VDD = 2 V

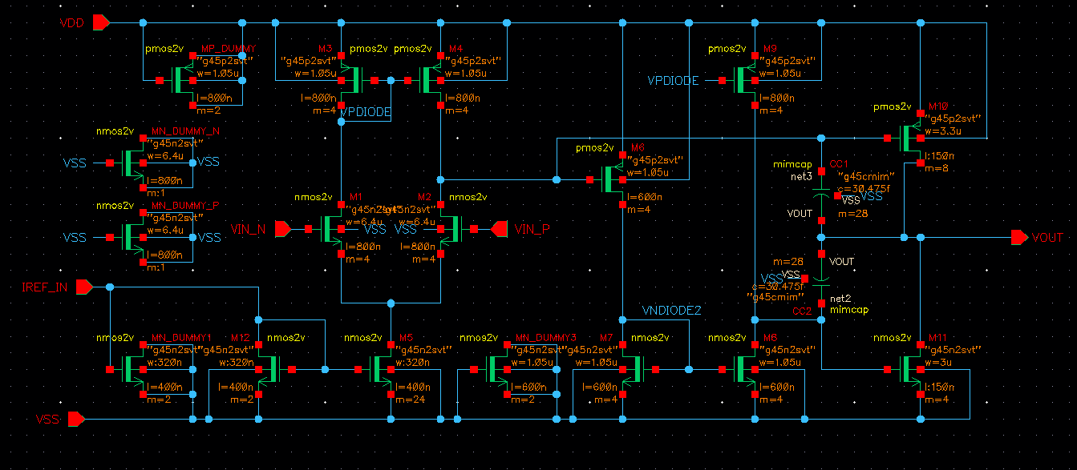

3 Stage Class-AB Common Source CMOS Op-Amp

This op-amp design features:

AOL Gain > 75 dB

Phase Margin ΦM > 50°

High Slew Rate > 20 V/µs

Low Offset < 1.5 mV

Unity-Gain Bandwidth

> 25 MHz

Low Power Consumption < 500 µW

Near Rail-to-Rail Output Swing (0.01 V to 1.99 V)

High CMRR and PSRR

& Low THD

Tested across PVT Corners and Monte Carlo

45 nm Technology with VDD = 2 V

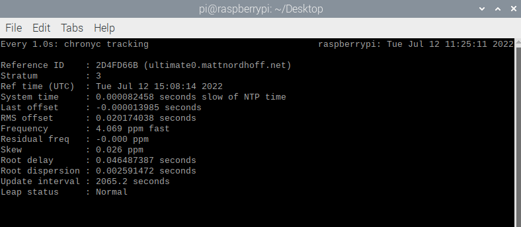

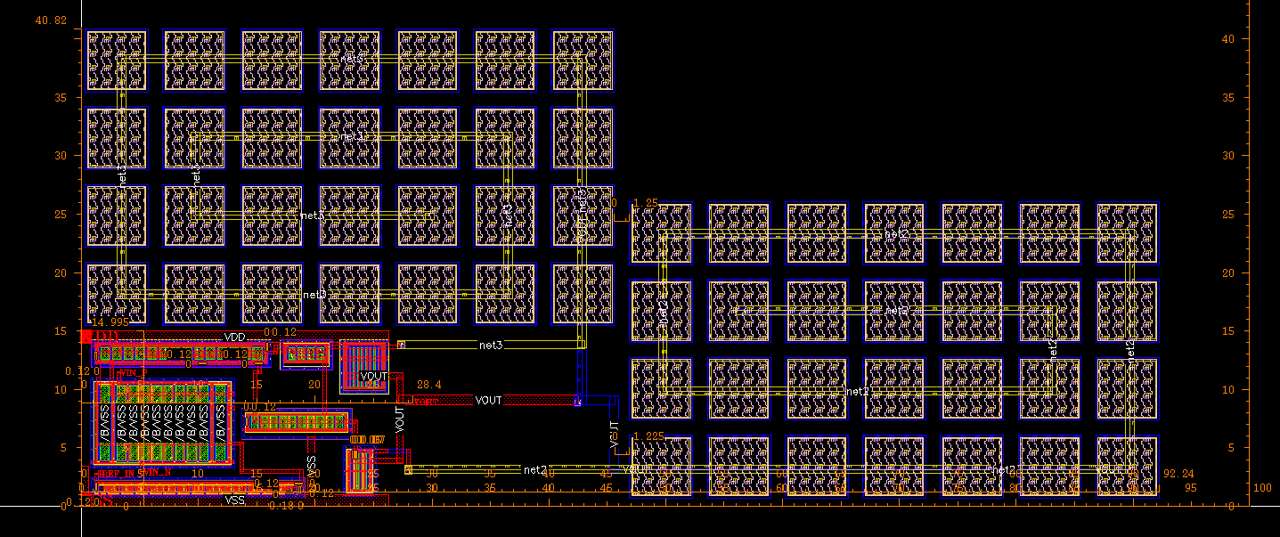

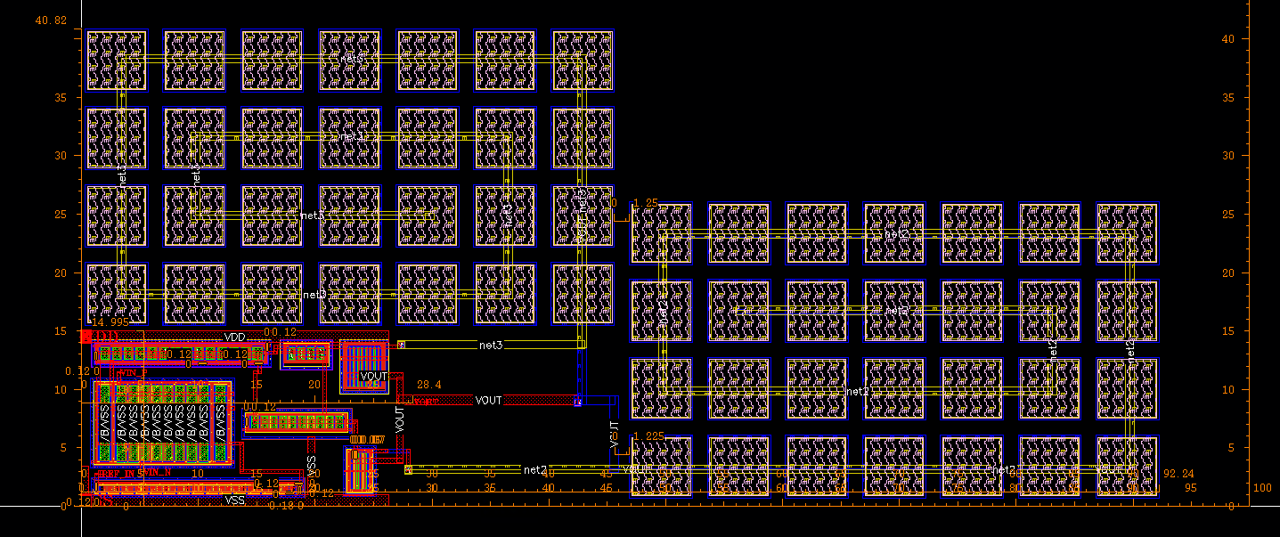

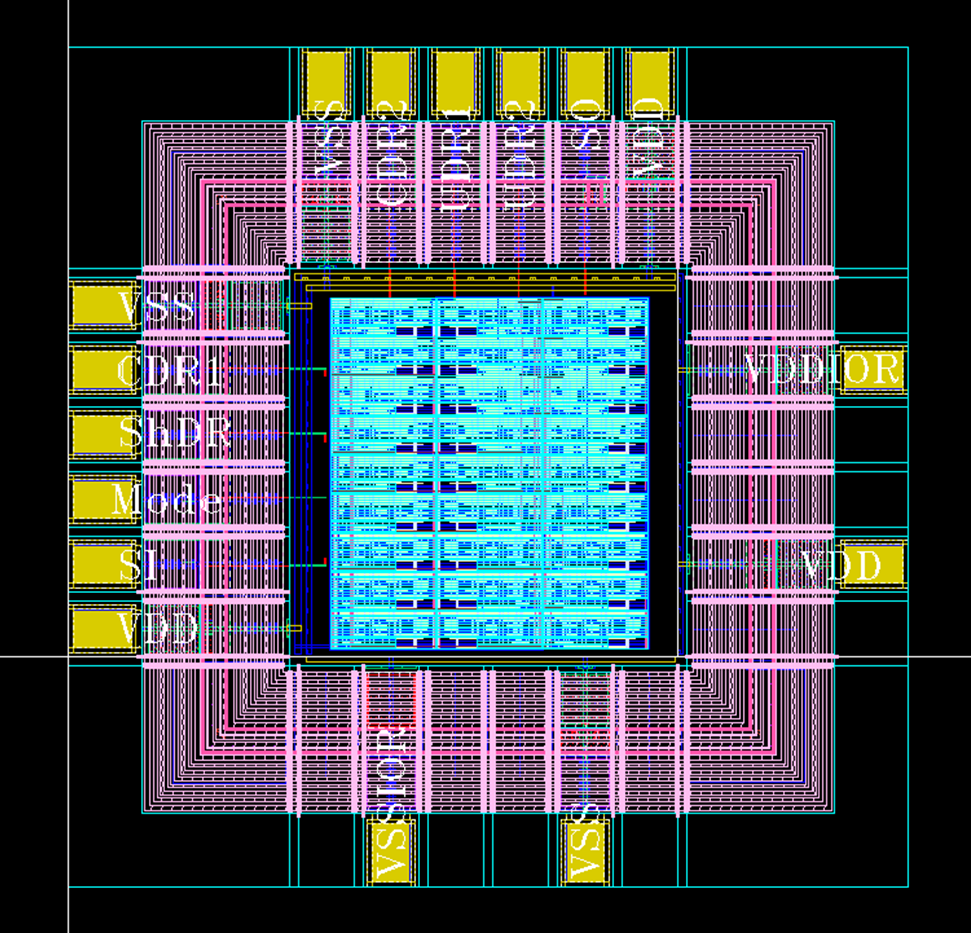

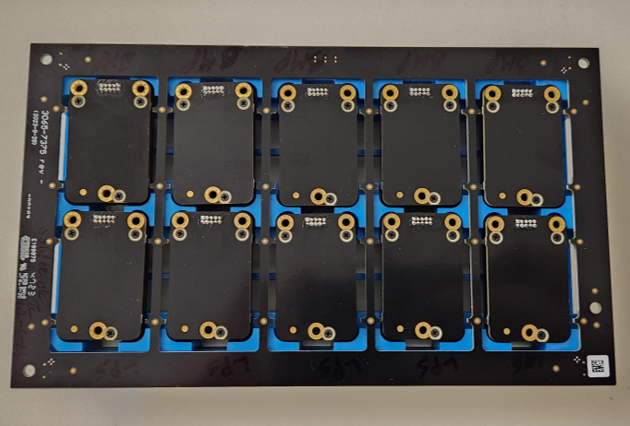

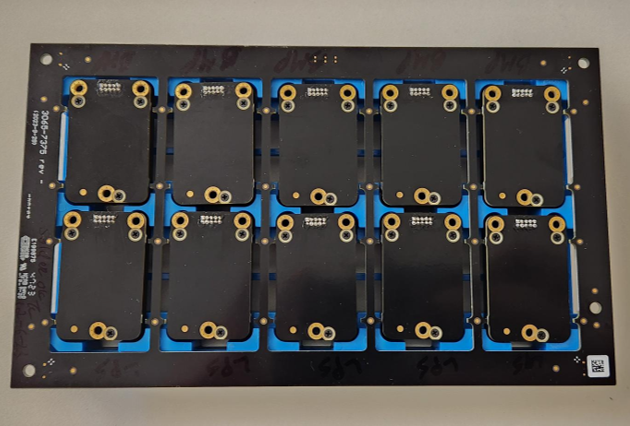

Quarter Pad-Frame Cell BSARRAY Design

This BSARRAY design features hierarchical components including:

TIEHI and TIELO Pull Cells

FA - Full Adder using 2 XNORs, 3 NANDs, and 1 INV

DFF - Rising Edge Triggered D Flip Flop

BSC - Boundary Scan Cell

BSR50 - 50-bit Boundary Scan Register

ADD16 - 16-bit Carry Select Adder

BSSUM - Combination of BSR50 and ADD16

256,684 Transistors using 45 nm Technology

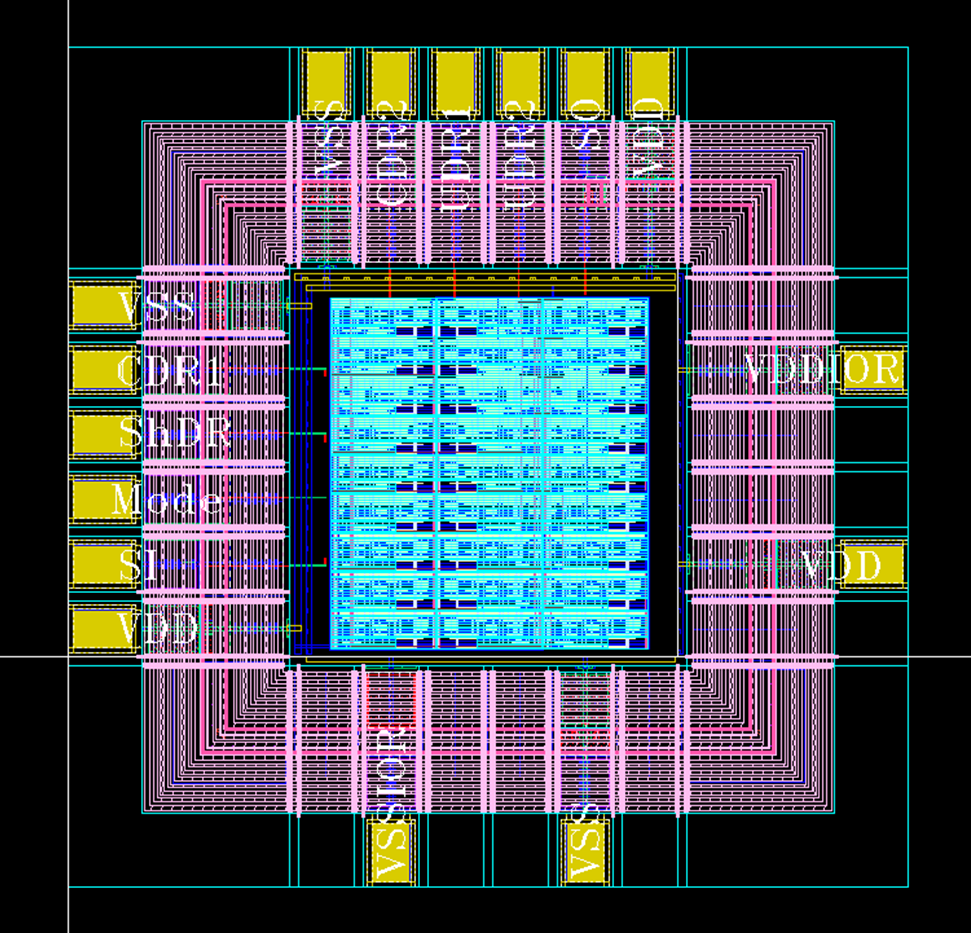

Quarter Pad-Frame Cell BSARRAY Design

This BSARRAY design features hierarchical components including:

TIEHI and TIELO Pull Cells

FA - Full Adder using 2 XNORs, 3 NANDs, and 1 INV

DFF - Rising Edge Triggered D Flip Flop

BSC - Boundary Scan Cell

BSR50 - 50-bit Boundary Scan Register

ADD16 - 16-bit Carry Select Adder

BSSUM - Combination of BSR50 and ADD16

256,684 Transistors using 45 nm Technology

LBIST Research Paper

This Logic Built-in Self Test (LBIST) Research paper discusses the following topics:

Fault Coverage Optimization

Testing Power Efficiency

Low-Power (LP) BIST Architecture

Weighted Pseudorandom Test-Pattern Generation (TPG) and Reseeding

Scan Segmentation and Weighted Scan Chains

Partioned Deterministic Compressed Tests

Applications in Digital Microfluidic Logic Gates, Telecom SoC Silicon Validation, and Wearout Diagnosis

Please inquire for further details

LBIST

Research Paper

This Logic Built-in Self Test (LBIST) Research paper discusses the following topics:

Fault Coverage Optimization

Testing Power Efficiency

Low-Power (LP)

BIST Architecture

Weighted Pseudorandom Test-Pattern Generation (TPG) and Reseeding

Scan Segmentation and Weighted Scan Chains

Partioned Deterministic Compressed Tests

Applications in Digital Microfluidic Logic Gates, Telecom SoC Si. Validation, and Wearout Diagnosis

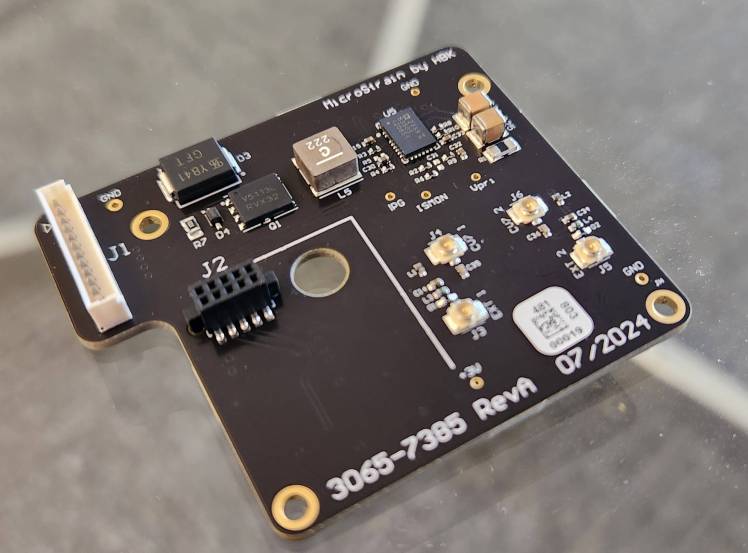

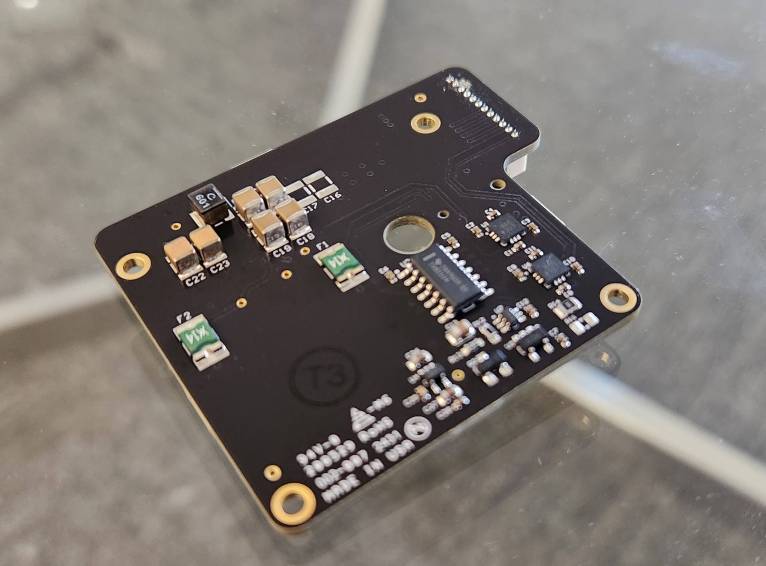

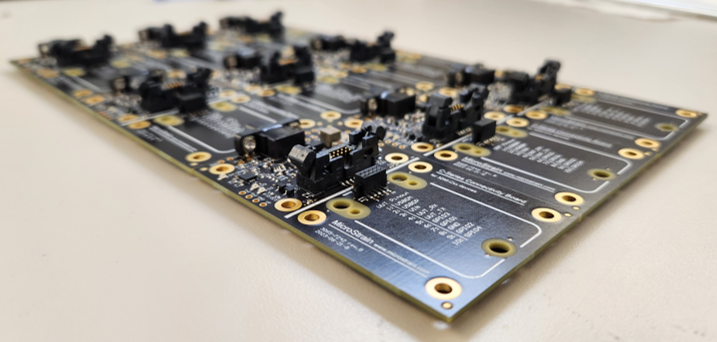

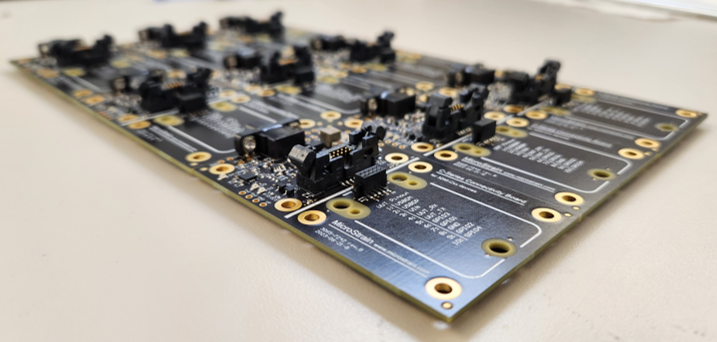

Industrial-Grade Daughter Board

This PCB Features:

Buck-Boost Converter

Low Dropout (LDO)

Reverse Polarity + ESD Protection

USB, GPIO, and RS-232 Peripherals

Hardware Signal Filtration

Transmission Lines with Bias Tee

Industrial-Grade Daughter Board

This PCB Features:

Buck-Boost Converter

Low Dropout (LDO)

Reverse Polarity

+ ESD Protection

USB, GPIO, and

RS-232 Peripherals

Hardware Signal Filtration

Transmission Lines

with Bias Tee

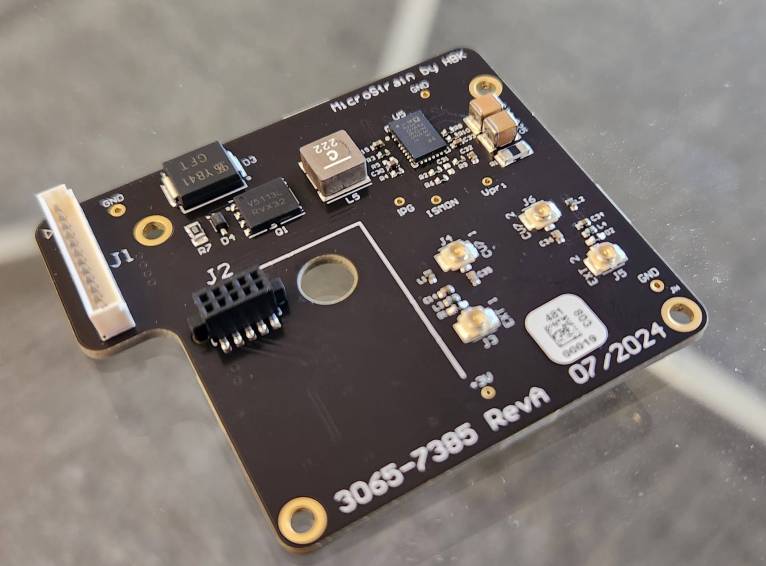

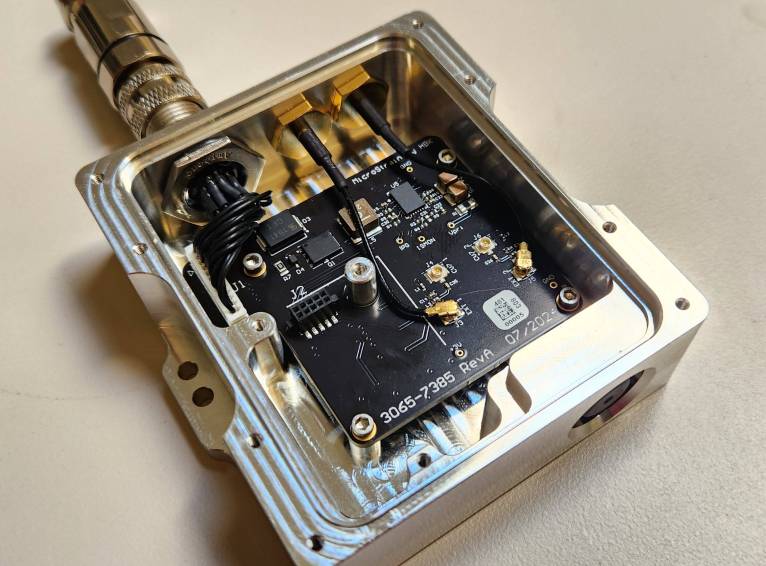

CV8 GNSS/INS Raptor Board

This PCB Features:

Buck Converter

Low Dropout (LDO)

ESD Protection

MEMS Inertial Navigation Unit (IMU)

Pressure Sensor

Magnetometer

USB, GPIO, and RS-232 Peripherals

Hardware Signal Filtration

LED Power Indicators + Test Points (TPs)

CV8 GNSS/INS Raptor Board

This PCB Features:

Buck Converter

Low Dropout (LDO)

ESD Protection

MEMS

Inertial Navigation Unit (IMU)

Pressure Sensor

Magnetometer

USB, GPIO, and

RS-232 Peripherals

Hardware Signal Filtration

LED Power Indicators

+ Test Points (TPs)

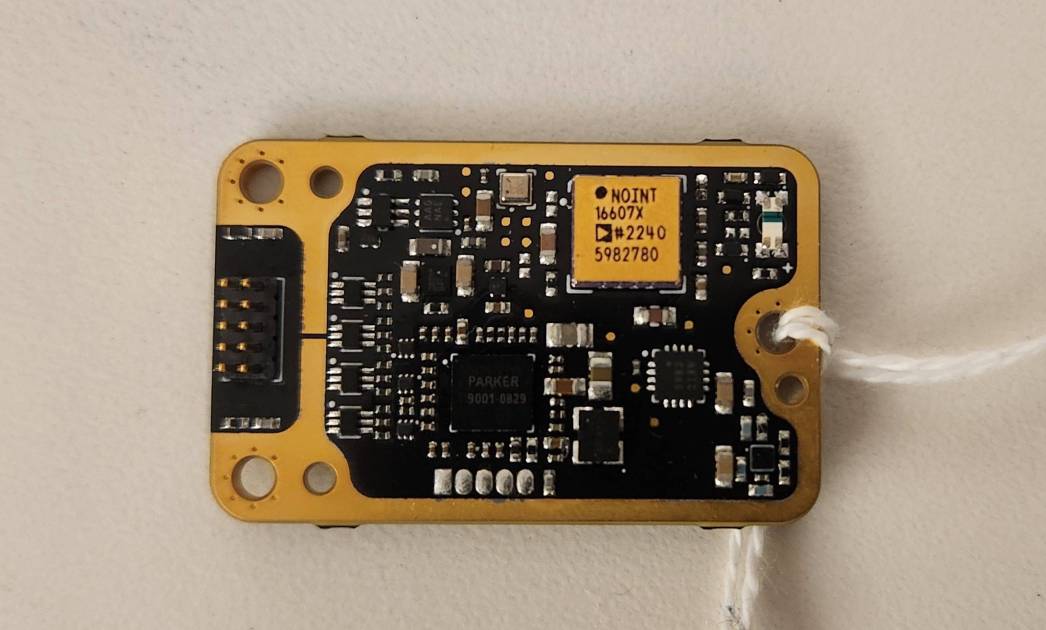

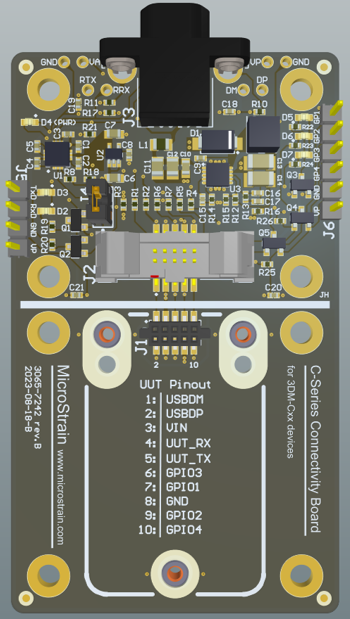

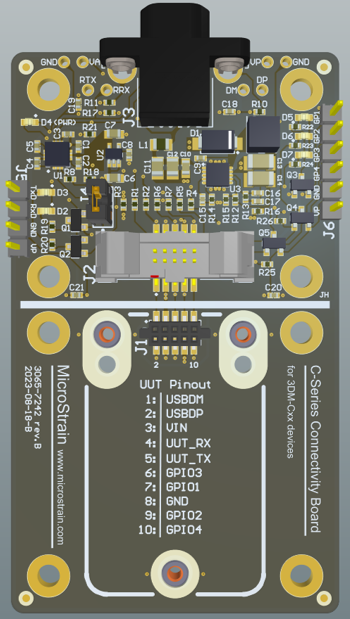

C-Series Connectivity Board

This PCB Features:

Low Dropout (LDO)

ESD Protection

USB, GPIO, and RS-232 Peripherals

Hardware Signal Filtration

LED Power Indicators + Test Points (TPs)

C-Series Connectivity Board

This PCB Features:

Low Dropout (LDO)

ESD Protection

USB, GPIO, and

RS-232 Peripherals

Hardware Signal Filtration

LED Power Indicators

+ Test Points (TPs)

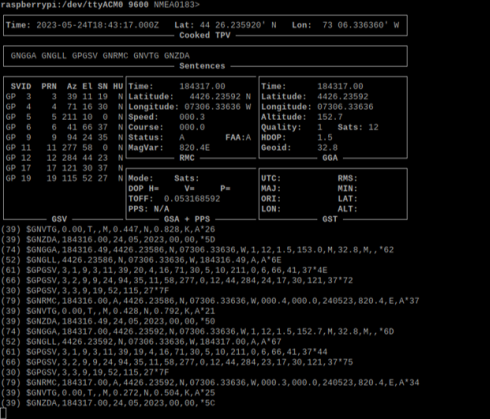

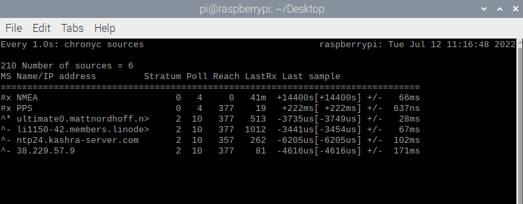

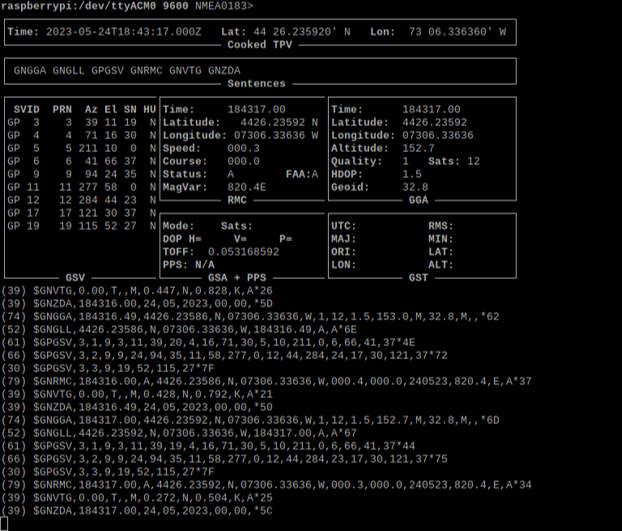

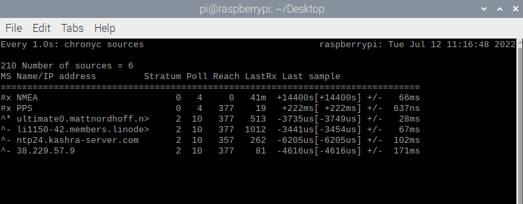

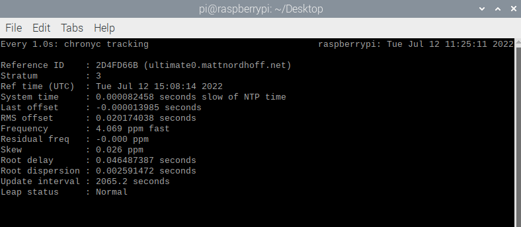

PPS Synchronization via NTP Clients

What was Done:

Programmatically Parsed NMEA Data

Supported Feature not present in Existing API

Sourced Time and GNSS/INS data from GQ7 as Host

PPS Synchronization with Stratum Servers

Ultra-low Latency of 400 ns

PPS Synchronization via NTP Clients